2024, 9(2)

e-ISSN: 2468-4376 https://jisem-journal.com/

#### **Research Article**

## A Novel Dual Leg Circuit Architecture for Synthesizing Variable Stepped Waveform at MLI Output for Extreme Fine Tuning of Harmonic Profile

Kaushal Bhatt<sup>1</sup>, Hemang Pandya<sup>2</sup>, Hiren Mehta<sup>3</sup>, Sandeep Chakravorty<sup>4</sup>, Nirali Upadhyay<sup>5</sup>, Ganesh Shingade<sup>6</sup>

1. 2.5 Electrical Engineering Department, Government Engineering College, Modasa (GECM),

Gujarat Technological University (GTU), Gujarat, India

<sup>3</sup> Electrical Engineering Department, Vishwakarma Government Engineering College (VGEC),

Gujarat Technological University (GTU), Gujarat, India

<sup>4</sup>Electrical Engineering Department, Indus Institute of Technology and Engineering (IITE)

Indus University, Gujarat, INDIA,

<sup>6</sup> Electrical Engineering Department, JNEC, MGM University, Chh.Sambhajinagar (MGMU), Maharashtra, India

#### **ARTICLE INFO**

#### ABSTRACT

Received: 18 Apr 2024 Accepted: 28 Jun 2024 **Introduction**: This article introduces a novel circuit architecture designed to synthesize accurate variable stepped waveforms using a dual leg structure in each phase. Stepped waveforms have become crucial in power electronics drives due to their numerous advantages. Existing literature highlights the effectiveness of stepped waveforms generated through various algorithms and inverter topologies. However, conventional equal-height steps do not accurately emulate the nature of a sine wave, which has a varying rate of change at different intervals.

**Objectives**: The main objective of this study is to develop a circuit architecture that can generate stepped waveforms with variable heights at the sides and peak, closely approximating a sine wave. The study aims to improve the harmonic profile and reduce Total Harmonic Distortion (THD) by implementing a novel dual leg structure in a three-phase cascaded H-bridge Multilevel Inverter (MLI).

**Methods**: The proposed architecture employs a dual leg structure per phase in a three-phase CHB-MLI simulated using MATLAB-SIMULINK. The circuit is designed to minimize redundant control points, thereby simplifying the hardware and lowering cost. To optimize the waveform quality, firing angles are calculated using a Genetic Algorithm (GA) and applied at the gate terminals of the inverter switches.

**Results**: Simulation results demonstrate that the proposed dual leg circuit architecture significantly enhances harmonic performance. By applying GA-optimized firing angles to the inverter, the system achieves a notable reduction in harmonics. Specifically, the THD is reduced by 12.6% compared to conventional approaches with fixed step heights.

**Conclusions**: The study confirms that integrating a dual leg architecture with variable stepped waveform synthesis and optimized firing angles effectively minimizes THD. This novel approach not only enhances waveform fidelity but also enables a cost-effective and hardware-efficient solution for power electronic applications.

Keywords: Multi level inverter, THD, Genetic Algorithm.

#### INTRODUCTION

Inverters have been the energy suppliers for decades, and many researchers are working on these devices to improve the output voltage profile and managing THD profile so that the lower order harmonics remain low and do not create unwanted phenomena such as cogging and crawling at the end connected inductive load [1][2].

Researchers have given attention to various modulation techniques to maintain harmonic profile such as selective harmonic elimination, sine triangle pulse width modulation, space vector modulation, and many more to mention

2024, 9(2) e-ISSN: 2468-4376 https://jisem-journal.com/

#### **Research Article**

as all these main techniques have their sub-methods for fine tuning in harmonic profile as required by the load [3],[4],[5].

In this article for synthesizing stepped waveform cascaded H-bridge inverter is taken into consideration as a 7-level inverter. Furthermore to help synthesize the waveform such that it eliminates lower-order harmonics, selective harmonic elimination is taken into consideration. The said method also helps limiting the electromagnetic interference in the vicinity. Due to the low-frequency operation of the selective harmonic elimination at gate terminals of the switches, the control circuit requirements are simple, robust and low-cost [3] [6]. In this article the use of combination of SHE PWM technique with cascaded H-bridge inverter fulfills requirement of eliminating cogging and crowling phenomena at end connected induction motor load with low cost control circuit.

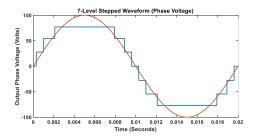

Figure 1. depicts a 7-level stepped waveform overlapped with a sine waveform in order to show the relative difference between the shape [7]. It can be seen that the steps are progressing at a particular angles [8], [9].

Figure 1. 7-level Stepped Voltage output at phase terminals with overlapping Sinusoidal waveform.

Many researchers have used various methods to find these firing angles [10], [11], [12], [13], [14] in the above said combination of CHB-MLI and SHE-PWM. In reference [14]the authors have used Genetic algorithm to find the optimum firing angles. In article [13] the authors have used hybrid Newton raphson and genetic algorithm technique. Bat algorithm is used in article [12] and in article [11] particle swarm optimization technique is used. In article [10] teacher learner-based algorithm is used for optimum firing angle calculations.

While keeping in view on such findings, some authors have also published research with variable step heights resembling the nature of sinusoidal wave forms. Sinusoidal waveforms are high sloppy at sides and the slop is less at the peak area [15]. To resemble the same phenomena the step heights should be high at sides and low at the top area. Article [16] represents the use of GA for finding firing angles and the angles are used with variable step wave forms. In the article [17] homotopy algorithm is used to solve the non-linear transcendental equations and variable step heights are formulated to optimize the harmonic profile. The same procedure as above is followed in reference [18] with PSO algorithm. In article [19] harmonic profile is managed by hybrid fuzzy-ABC algorithm with variable step heights. In article [20] the authors have used fuzzy -PSO algorithm for the selection of firing angle and variable step heights. In article [21] TLBO algorithm is used with alterable DC source for line voltage THD reduction. In [22] authors have used a variable DC source with an Imperialist Competitive Algorithm for harmonic profile optimization.

#### **RESEARCH GAP:**

All of the above articles have used alterable DC sources in order to make the output very near to pure sinusoidal waveshape and reduce the lower-order harmonics. Some of the articles have used MATLAB Simulink for the verification of the idea of using alterable DC sources and some have verified the same using hardware. While dealing with this study it is found that the variable DC sources which give altering step heights in positive cycle are not able to give the same step height in the negative half cycle due to the obvious reason that while the circuit is in working mode supply polarity can't be changed easily. If an attempt is taken to change the polarity while the circuit is working, it may cause serious instability and volatility in the supply system. As a remedial step to the above problem a novel dual leg structure is suggested with reduced number of switches to obtain the output with equal alterable DC voltage step heights in positive as well as negative cycles.

2024, 9(2)

e-ISSN: 2468-4376 https://jisem-journal.com/

#### **Research Article**

#### **Article structure:**

This article is structured as follows: section 2 presents brief theory of stepped waveform and the nonlinear transcendental equations representing them using MATLAB -SIMULINK. Section 3 represents the use of novel dual leg structure for synthesizing actual alterable DC source stepped waveforms. Section 4 presents the result discussion followed by conclusion, future scope and references.

## 1. CASCADED H-BRIDGE INVERTER AND REQUIREMENT OF ALTERABLE STEPS

#### 1.1. Stepped waveforms and their mathematical modelling:

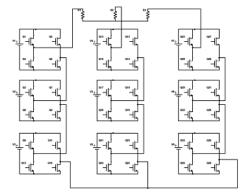

For the sake of study of the present concept a 3-phase, 7-level cascaded H-bridge inverter is taken for consideration. The simulation structure for the same is depicted in Figure 2, as such the study is valid for any kind of multilevel inverter. The output phase voltage steps can be calculated as Z = 2K+1, where Z is a number of steps and K is a number of DC sources in a single leg of a three-phase system as shown in Figure 3 [23].

The line voltage steps are dependent on the firing angles of switches, and it should also be noted that the phase and line voltage equations are dependent on number of steps.

Figure 2. 3-Phase Seven-Level Cascaded H-bridge Multilevel Inverter

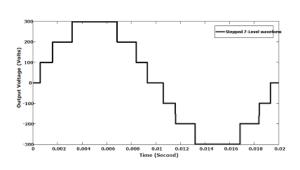

Figure 3. 1-Phase Seven-Level Synthesized Waveform at the output of CHB-MLI

The mathematical modeling of the output stepped voltage can be presented with the help of Fourier series representation. Equation 1, represents the basic fourier transform of the stepped waveform shown in Figure 2[24].

$$v(wt) = a_0 + \sum_{n=1}^{\infty} \left[ a_n \cos(nwt) + b_n \sin(nwt) \right]$$

(1)

In the present study the load in considered to be balanced in all three phases as well as the supply is considered to have quarter wave and half wave symmetry. So the DC component ao and cosine coefficient an becomes zero. The remaining component bn can be shown by equation 2 as,

$$b_n = \frac{4V_{DC}}{n\pi} \left[ \cos(n\alpha_1) + \cos(n\alpha_2) + \cos(n\alpha_3) \right]$$

(2)

The final stepped output voltage equations can be given as shown in equation 3.

$$v(wt) = \sum_{n=1,3,5,\dots}^{\infty} \frac{4V_{DC}}{n\pi} \left[\cos(n\alpha_1) + \cos(n\alpha_2) + \cos(n\alpha_3)\right] \sin(nwt)$$

(3)

2024, 9(2)

e-ISSN: 2468-4376 https://jisem-journal.com/

#### **Research Article**

# 1.2. 3-phase 7-level Cascaded H-bridge inverter harmonic profile improvement with fixed DC source using selective harmonic elimination.

As the name suggests, selective harmonic elimination eliminates selected harmonics. Lower order harmonics that cause cogging and crawling effects can be eliminated with the help of this method. Following equations 4 to 9 which are derived from equations 1 to 3, are the equations which can be used in a fitness function which is intern to be treated with an optimization method such as a genetic algorithm [25].

## Selective harmonic elimination equation set [reference 101, 102]

$$\cos(\alpha_1) + \cos(\alpha_2) + \cos(\alpha_3) = 3M \tag{4}$$

$$\cos(\alpha_1) + \cos(\alpha_2) + \cos(\alpha_3) = 3M \tag{5}$$

$$\cos(7\alpha_1) + \cos(7\alpha_2) + \cos(7\alpha_3) = 0 \tag{6}$$

$$\cos(7\alpha_1) + \cos(7\alpha_2) + \cos(7\alpha_3) = 0 \tag{7}$$

where,

M = modulation Index

$\alpha_1, \alpha_2, \alpha_3$  = firing angles related to each step in the 7-level inverter

## Fitness function [reference 101, 102]:

Fitness Function =

$$(10 \times |h_1 - 3M|) + (THD/10)$$

(8)

Here,

$$THD = \sqrt{\left(\frac{\boldsymbol{h}_5}{5}\right)^2 + \left(\frac{\boldsymbol{h}_7}{7}\right)^2 + \left(\frac{\boldsymbol{h}_{11}}{11}\right)^2}$$

(9)

Where,

$$h_1 = \cos(\alpha_1) + \cos(\alpha_2) + \cos(\alpha_3) \tag{10}$$

$$h_5 = \cos(5\alpha_1) + \cos(5\alpha_2) + \cos(5\alpha_3) \tag{11}$$

$$h_7 = \cos(7\alpha_1) + \cos(7\alpha_2) + \cos(7\alpha_3) \tag{12}$$

$$h_{11} = \cos(11\alpha_1) + \cos(11\alpha_2) + \cos(11\alpha_3)$$

(13)

$$M = \text{modulation index} = \frac{V_1}{\left(\frac{12V_{DC}}{\pi}\right)}$$

(14)

Derivation of the SHE equations and fitness function can be learned from references [1], [3], [26], the same is not derived for limiting the size of the article.

2024, 9(2) e-ISSN: 2468-4376 https://jisem-journal.com/

#### **Research Article**

## Optimization of the fitness function and finding optimized firing angles:

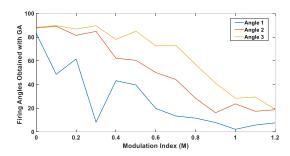

The above fitness function is optimized using genetic algorithm with parameters depicted in table 1 and the firing angle findings are found as shown in figure 4.

Table 1. Simulation parameter for running GA on MATLAB

|    | Algorithm Simulation Parameters                         | Simulation Parameters values |

|----|---------------------------------------------------------|------------------------------|

|    | Number of iterations                                    | 80                           |

|    | Population size                                         | 20                           |

| GA | Mutation rate                                           | <0.06                        |

|    | Upper and lower bound considering quarter-wave symmetry | 0° to 90°                    |

|    | Simulation code running platform                        | MATLAB                       |

|    | Input DC source fixed value for each H-bridge           | 12 V                         |

Figure 4. Firing angles obtained through Genetic Algorithm

## 1.3 Requirements of alterable DC sources for fine tuning the harmonic profile

The firing angles obtained from optimization process have been fed to the MATLAB-Simmulink model (shown in Figure 2) with fixed DC sources is depicted in following figures.

Here these results are deliberately put in this section for the sake of understanding of readers. It can be seen here that, with the help of optimization process 5th, 7th and 11th harmonics are almost eliminated. It should be kept in notice that the triplen harmonics are automatically eliminated in the three-phase system due to 120-degree phase shift and balanced nature of supply and load.

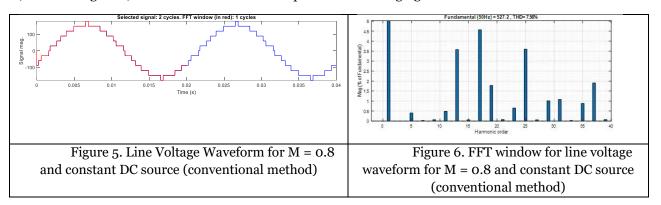

Figure 5 and 6 show line voltage waveform and THD profile. Here in the present study, it can be observed that the phase voltage (as shown in Figure 3) is having fixed step size and if the step size could have been alterable and if somehow the step heights can be made proportional to the rate of change of sine wave then the phase stepped voltage waveform could have been closer to sinusoidal shape.

2024, 9(2)

e-ISSN: 2468-4376 https://jisem-journal.com/

#### **Research Article**

The study of the closeness of stepped waveform to the sinusoidal waveform using an alterable DC source and the architecture of the hardware for the same is discussed in the next section.

## 2. 3-phase 7-level Cascaded H-bridge multilevel inverter architecture with alterable DC sources.

#### 2.1 Variable step height requirements and calculation: -

Article [17], [18], [19], [20], [21], [22], [23] shows that alterable DC sources are always beneficial and provides near sinusoidal waveform. Many such articles have shown their own way of calculating the heights of each step. In this article, the study given in reference [15] is taken for consideration and understating of variable step heights.

As per article [15], [21] after the rigorous calculation each fixed DC source values are to be multiplied by a constant number. In the present study the fixed DC source values are taken to be 30 V, and the proposed hardware is having three H-bridges in each leg to produce 7 level phase output waveforms. In the given study the coefficients a1, a2 and a3 taken from reference [21] are 0.81, 0.78 and 0.73 to be multiplied with each DC source. The variable DC sources obtained from the multiplication process is tabulated below in table 2.

Table 2. Variable DC source values

| DC source number | Multiplication factor [555] | Alterable DC source value |

|------------------|-----------------------------|---------------------------|

| Vdc1             | 0.81                        | 24.3                      |

| Vdc2             | 0.78                        | 23.4                      |

| Vdc3             | 0.73                        | 21.9                      |

As discussed earlier these variable DC source values are to be put in to the simulation model and hardware, so that the improvement in the THD can be observed. As debated earlier in the introduction section, many articles have shown the calculation of the variable DC sources but the hardware structure which can promise the improvement in THD is not discussed in most articles. In the following section hardware architecture, which can be used to peruse the proposed study is explained in detail.

## 2.2 3-phase 7-level novel dual leg structure for variable step heights.

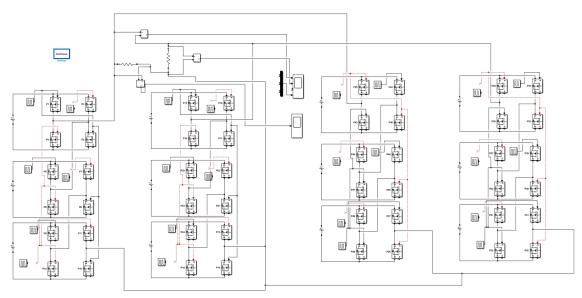

It is always difficult to produce variable step height, that too in positive as well as negative cycles. It is obvious that a circuit can be set to produce variable step height in positive cycle but the same supply hierarchy cannot be used in negative cycle. To solve the above problem a dual leg structure is proposed in this article. The architecture uses dual leg structure as depicted in figure 7. Here one of the legs works for a positive half cycle and the other works in negative half cycle.

2024, 9(2)

e-ISSN: 2468-4376 https://jisem-journal.com/

## **Research Article**

Figure 7. 3-phase 7-level novel dual leg structure for variable step heights created and simulated with MATLAB-SIMULINK (2019-b)

It can be clearly seen that in the given structure the control points are reduced such that the redundant control points are eliminated. To accommodate the architecture in a printable area and clarity of function of the circuit only two phases are shown. The proposed circuit is given firing angles as suggested in article [7] and the switching sequence for positive and negative cycles are depicted in the Table 3. The results are discussed in the next section.

Table 3. Switching sequence for positive and negative qurter cycles

| Positive cycle      |              | Negative cycle      |              |

|---------------------|--------------|---------------------|--------------|

| Voltage step height | Firing Angle | Voltage step height | Firing Angle |

| 24.3                | 5.71         | -24.3               | 180+5.71     |

| 23.4                | 17.18        | -23.4               | 180+17.18    |

| 21.9                | 35.91        | -21.9               | 180+35.91    |

#### SIMULATION RESULTS AND DISCUSSION

In this section results are discussed for one of the competent modulation index o.8. in most of the cases with most artificial techniques modulation index o.8 gives better results. Results are compared for fixed step heights and variable step heights for the given modulation index.

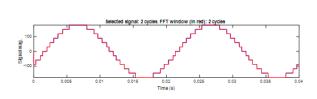

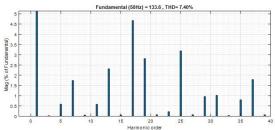

Figure 5 and Figure 6 show the waveform and THD profile for M=0.8 and fixed step height. Figure 10 and 11 show the waveform and THD profile for M=0.8 and variable step height.

Figure 8. Line Voltage Waveform for M = 0.8 and optimized DC source (after application of ratio rule)

Figure 9. FFT window for line voltage waveform for M = 0.8 and optimized DC source (after application of ratio rule)

2024, 9(2)

e-ISSN: 2468-4376 https://jisem-journal.com/

#### **Research Article**

Table 4, below shows the effect of using duel leg structure in fine tuning of the harmonic profile.

Table 4. Comparison between simulated and hardware results for M= 0.8.

| Modulation Index                                               | Simulation result of line<br>voltage THD |

|----------------------------------------------------------------|------------------------------------------|

| M = 0.8 (Constant DC sources)                                  | 7.56 %                                   |

| M = 0.8 (Optimized DC<br>sources after applying<br>ratio rule) | 7.40 %                                   |

Above Figures 8, 9 and table 3, show the superiority of dual leg structure for getting extreme reduction and fine-tuning of harmonic profile. Maximum reduction is seen in the case of M = 0.7, where the reduction is seen to be as good as 12.60 %.

#### **CONCLUSIONS**

In the present study 3-phase 7-level inverter is considered for harmonic profile improvement. Two groups of researchers have given various methods for harmonic profile improvement using fixed step height and variable step height. In most of the study, it is observed that for any modulation index value, the variable step height waveforms always give better results. It is also observed that in most of the literature several methods are discussed related to finding of variable step heights, and the actual circuit structure which synthesizes the variable step heights is not discussed anywhere.

In the present study, a dual-leg circuit architecture is discussed in section 3, which is used with pre-defined method of finding variable step heights. It is observed that the proposed architecture provides seamless experience in getting variable step heights at output terminals of the 3-phase 7-level inverter as depicted in section 4. For each modulation index, variable step height waveforms always gave better results than fixed step heights.

To limit the size of the article hardware implementation is omitted here and that is to be covered in the next part of this research paper in the same journal.

#### REFRENCES

- [1] M. A. Memon, S. Mekhilef, M. Mubin, and M. Aamir, "Selective harmonic elimination in inverters using bio-inspired intelligent algorithms for renewable energy conversion applications: A review," *Renewable and Sustainable Energy Reviews*, vol. 82. Elsevier Ltd, pp. 2235–2253, Feb. 01, 2018. doi: 10.1016/j.rser.2017.08.068.

- [2] Noorul Islam Centre for Higher Education. Department of Electrical and Electronics Engineering, IEEE Electron Devices Society. India Chapter, and Institute of Electrical and Electronics Engineers, *Proceedings of IEEE International Conference on Circuits, Power and Computing Technologies : ICCPCT-2016 on 18th & 19th March 2016.*

- [3] M. S. A. Dahidah, G. Konstantinou, and V. G. Agelidis, "A Review of Multilevel Selective Harmonic Elimination PWM: Formulations, Solving Algorithms, Implementation and Applications," *IEEE Trans Power Electron*, vol. 30, no. 8, pp. 4091–4106, 2015, doi: 10.1109/TPEL.2014.2355226.

- [4] A. Ajami, M. R. J. Oskuee, and A. O. Mokhberdoran, "Implementation of novel technique for selective harmonic elimination in multilevel inverters based on ICA," *Advances in Power Electronics*, vol. 2013, 2013, doi: 10.1155/2013/847365.

- [5] Zhongguo-Diangong-Jishu-Xuehui, IEEE Power Electronics Society, IEEE International Power Electronics and Motion Control Conference (IPEMC) 7 2012.06.02-05 Harbin, and IEEE Energy Conversion Congress and Exposition (ECCE Asia) 2012.06.02-05 Harbin, 7th International Power Electronics and Motion Control Conference (IPEMC), 2012 2-5 June 2012, Harbin, China; [also referred to as] ECCE Asia [as a part of ECCE (IEEE Energy Conversion Congress and Exposition) worldwide series].

2024, 9(2) e-ISSN: 2468

e-ISSN: 2468-4376 https://jisem-journal.com/

#### **Research Article**

- [6] M. S. A. Dahidah and V. G. Agelidis, "Selective harmonic elimination PWM control for cascaded multilevel voltage source converters: A generalized formula," *IEEE Trans Power Electron*, vol. 23, no. 4, pp. 1620–1630, Jul. 2008, doi: 10.1109/TPEL.2008.925179.

- [7] K. Bhatt and S. Chakravorty, "International Journal of Computing and Digital Systems A Comparative Study on Performance of Fitness Functions for Harmonic Profile Improvement using Parameter-less AI Technique in Multilevel Inverter for Electrical Drives." [Online]. Available: http://journals.uob.edu.bh

- [8] I. I. S. B. Indian Institute of Technology (Kharagpur, I. I. E. in M. and B. S. S. C. Indian Institute of Technology (Kharagpur, I. I. S. P. S. S. B. C. Indian Institute of Technology (Kharagpur, Institute of Electrical and Electronics Engineers. Kharagpur Section, I. I. A. J. S. B. C. Indian Institute of Technology (Kharagpur, and Institute of Electrical and Electronics Engineers. Women in Engineering Affinity, 2016 IEEE Students' Technology Symposium: 30 September 2 October 2016, IIT Kharagpur.

- [9] M. Gnana Sundari, M. Rajaram, and S. Balaraman, "Application of improved firefly algorithm for programmed PWM in multilevel inverter with adjustable DC sources," *Applied Soft Computing Journal*, vol. 41, pp. 169–179, Apr. 2016, doi: 10.1016/j.asoc.2015.12.036.

- [10] M. Mardaneh and F. Golestaneh, "Harmonic optimization of diode-clamped multilevel inverter using teaching-learning-based optimization algorithm," *IETE J Res*, vol. 59, no. 1, pp. 9–16, 2013, doi: 10.4103/0377-2063.110616.

- [11] V. K. Gupta and R. Mahanty, "Optimized switching scheme of cascaded H-bridge multilevel inverter using PSO," *International Journal of Electrical Power and Energy Systems*, vol. 64, pp. 699–707, 2015, doi: 10.1016/j.ijepes.2014.07.072.

- [12] K. Ganesan, K. Barathi, P. Chandrasekar, and D. Balaji, "Selective Harmonic Elimination of Cascaded Multilevel Inverter Using BAT Algorithm," *Procedia Technology*, vol. 21, pp. 651–657, 2015, doi: 10.1016/j.protcy.2015.10.078.

- [13] A. Parkash, S. L. Shimi, S. Chatterji, M. E. Student, and P. / Head, "Harmonics Elimination in Cascade Multilevel Inverters Using Newton-Raphson and Genetic Algorithm," 2014. [Online]. Available: https://www.researchgate.net/publication/265509280

- [14] IEEE Chilecon 2015 Santiago de Chile et al., Proceedings of IEEE Chilecon2015 held inUniversidad Central de Chile, Santiago, Chile, October 28-30, 2015: IEEE Chilean Conference on Electrical, Electronics Engineering, Information and Communication Technologies. IEEE, 2015.

- S. H. Fathi, M. G. H. Aghdam, A. Zahedi, and G. B. Gharehpetian, "Optimum regulation of DC sources in [15] cascaded multi-level inverters," COMPEL - The International Journal for Computation and Mathematics in Electrical and *Electronic* Engineering, vol. 28, no. 2009, doi: 2, pp. 385-395, 10.1108/03321640910929281.

- [16] M. Sabahi, A. R. M. Iranaq, K. M. Bahrami, K. M. Bahrami, and M. B. B. Sharifian, "Harmonics elimination in a multilevel inverter with unequal DC sources using genetic algorithm," in *2011 International Conference on Electrical Machines and Systems, ICEMS 2011*, 2011. doi: 10.1109/ICEMS.2011.6073451.

- [17] M. G. H. Aghdam, S. H. Fathi, and G. B. Gharehpetian, "Elimination of Harmonics in a Multi-Level Inverter with Unequal DC Sources Using the Homotopy Algorithm."

- [18] A. K. Al-Othman and T. H. Abdelhamid, "Elimination of harmonics in multilevel inverters with non-equal dc sources using PSO," *Energy Convers Manag*, vol. 50, no. 3, pp. 756–764, Mar. 2009, doi: 10.1016/j.enconman.2008.09.047.

- [19] M. Malarvizhi and I. Gnanambal, "Harmonics elimination in multilevel inverter with unequal DC sources by fuzzy-ABC algorithm," *Journal of Experimental and Theoretical Artificial Intelligence*, vol. 27, no. 3, pp. 273–292, May 2015, doi: 10.1080/0952813X.2014.930596.

- [20] M. Malarvizhi and I. Gnanambal, "An integrated technique for eliminating harmonics of multilevel inverter with unequal DC sources," *International Journal of Electronics*, vol. 102, no. 2, pp. 293–311, Feb. 2015, doi: 10.1080/00207217.2014.896049.

- [21] M.-R. Jannati-Oskuee, "Optimization of Line voltage THD in Multilevel Inverter"s with Alterable DC Links using TLBO Optimization of Line voltage THD in Multilevel Inverter's with Alterable DC Links using TLBO," 2017. [Online]. Available: www.IC-EE.ir

2024, 9(2)

e-ISSN: 2468-4376 https://jisem-journal.com/

#### **Research Article**

- [22] F. Bilimleri Dergisi, M. Salimi, A. Aghazadeh, F. Arasteh, T. Yousefi, and S. Mehdi Mirkazemi NIYARAGH, "Cumhuriyet Üniversitesi Fen Fakültesi Using Imperialist Competitive Algorithm to optimize the Switching Angle of the multilevel Inverter in order to Eliminate Low Order Harmonics Considering the Variation of DC Voltage Sources," *Cumhuriyet University Faculty of Science Science Journal (CSJ)*, vol. 36, no. 6, p. 36, 2015, [Online]. Available: http://dergi.cumhuriyet.edu.tr/ojs/index.php/fenbilimleri©2015

- [23] N. Farokhnia, H. Vadizadeh, S. H. Fathi, and F. Anvariasl, "Calculating the formula of line-voltage THD in multilevel inverter with unequal DC sources," *IEEE Transactions on Industrial Electronics*, vol. 58, no. 8, pp. 3359–3372, Aug. 2011, doi: 10.1109/TIE.2010.2089938.

- [24] N. Yousefpoor, S. H. Fathi, N. Farokhnia, and H. A. Abyaneh, "THD minimization applied directly on the line-to-line voltage of multilevel inverters," *IEEE Transactions on Industrial Electronics*, vol. 59, no. 1, pp. 373–380, Jan. 2012, doi: 10.1109/TIE.2011.2143373.

- [25] K. Bhatt and S. Chakravorty, "Optimum regulation of THD profile in multilevel inverter using parameter-less AI technique for electrical vehicle application."

- [26] K. Bhatt and S. Chakravorty, "Mitigation of Harmonics from Output of Cascaded H Bridge Multilevel Inverter Using SHE PWM and AI Technique: A Review," *Recent Advances in Electrical & Electronic Engineering* (Formerly Recent Patents on Electrical & Electronic Engineering), vol. 13, no. 7, pp. 952–968, Feb. 2020, doi: 10.2174/2213111607666200214121450.